Toward 5G RAN virtualization by Intel and Astri

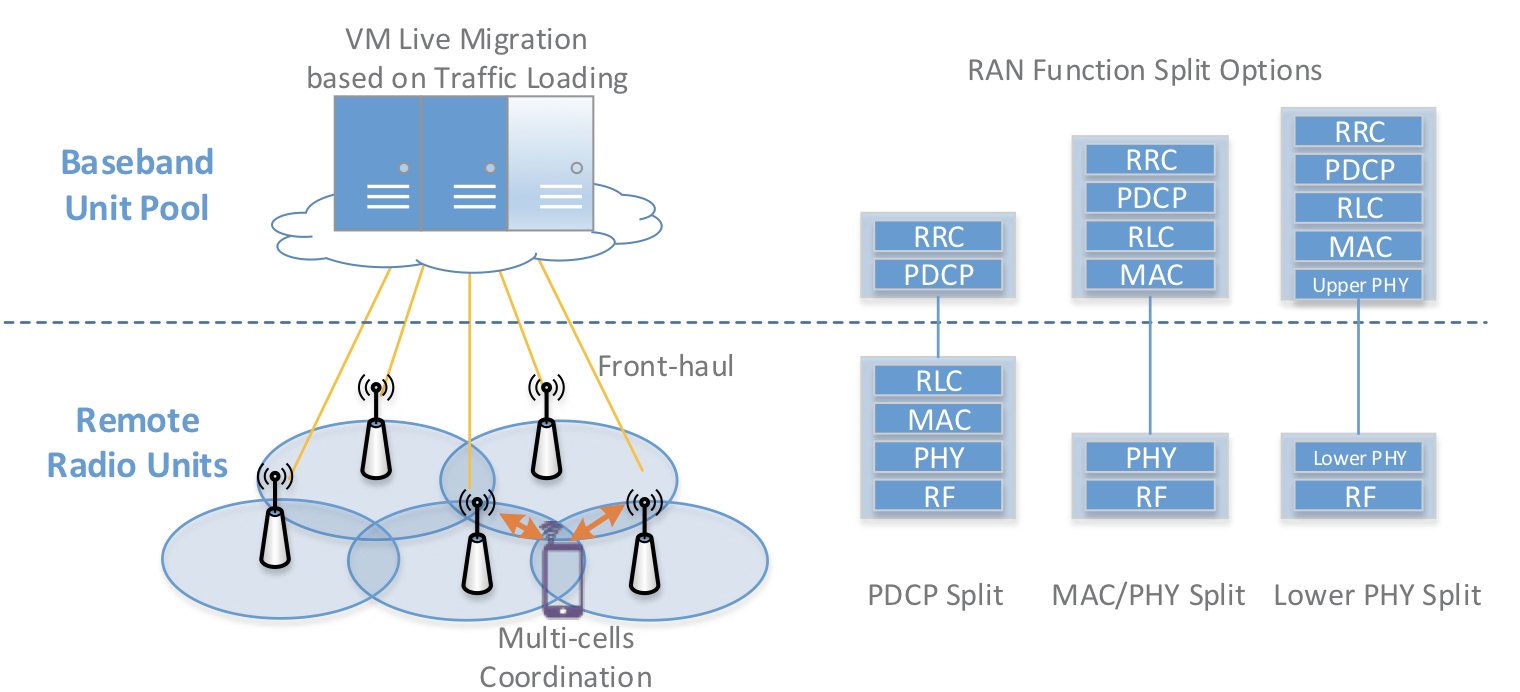

Flexible architecture

Modular PHY processing architectures

- PDCP Split

- MAC/PHY Split - HARQ processing in RRU(How???)

- Lower PHY Split - High FB overhead but smallest packet latency.

- Good for JT and JR for COMP

- Good for Massive MIMO and Ultra low-latency communication(Why?)

- FAPI based MAC/PHY communication

- L1 adaptation layer for MAC/PHY split (and Lower PHY Split?)

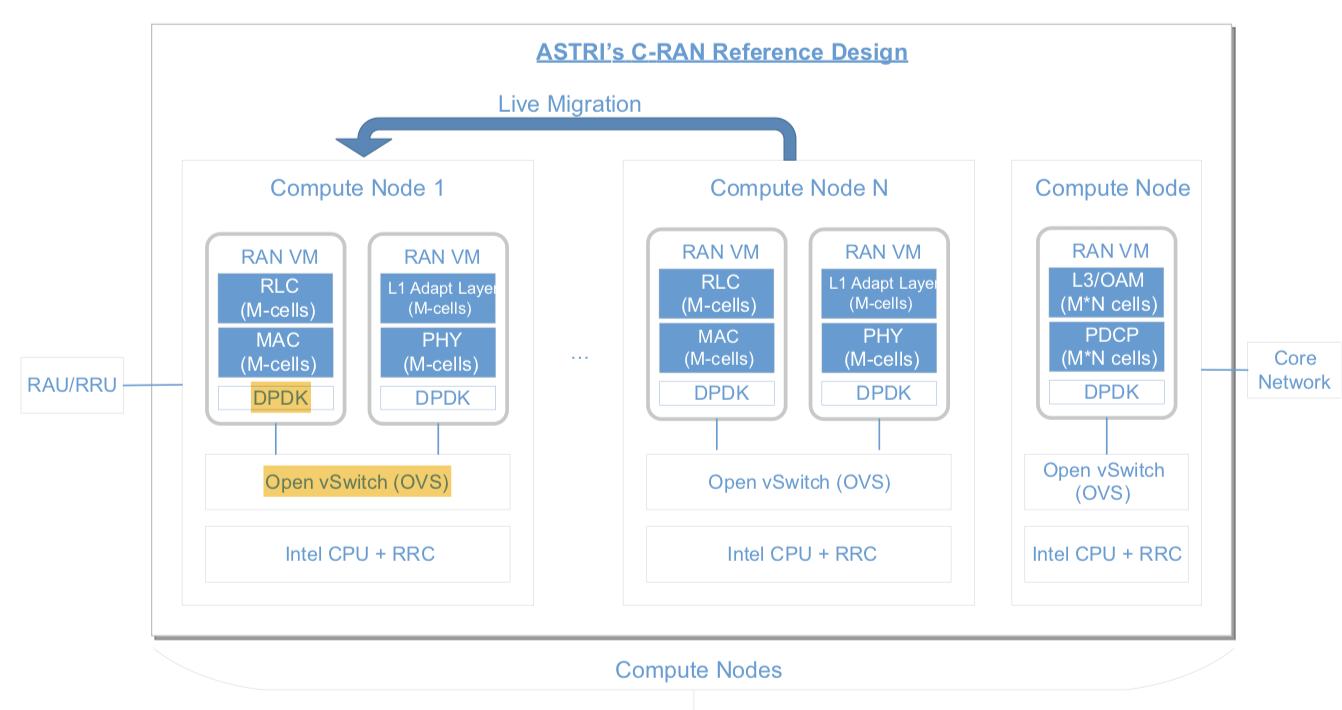

MAC/PHY split in one CPU

- MAC/PHY split in one machine but netrwork based MAC/PHY communication over OVS

Virtual Cell

- A group of physical cells form a

Virtual Cellwhich does not require HO between the physical cells.

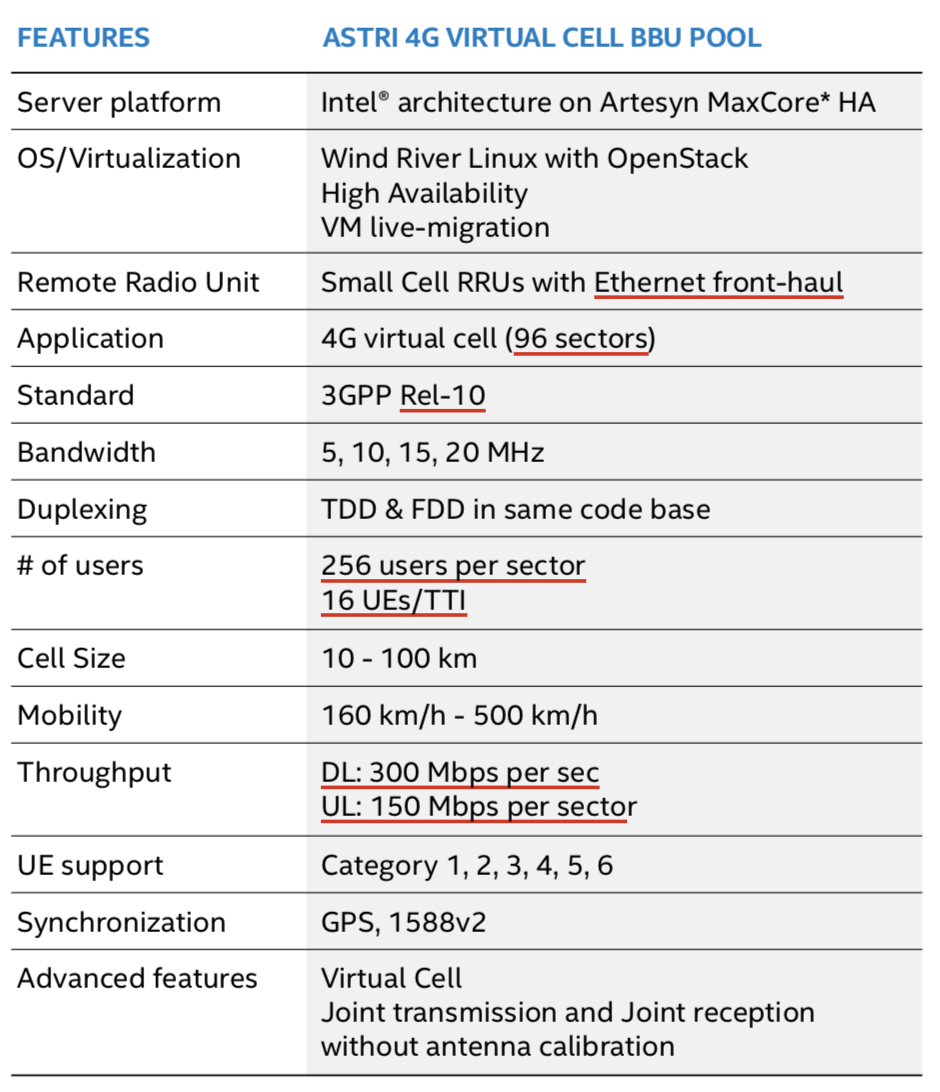

Technical Specification

Commercial L1 reference design

Artesyn MacCore

- Xeon-D - 8 or 12 core/CPU * 2 CPU/slot * 15 slots

- https://www.artesyn.com/computing/products/product/max-core

- https://www.artesyn.com/computing/assets/maxcore_platform_ds_1484017329.pdf�